Chapter 15

## ARM – Architecture, Programming and Development Tools

Microcontrollers-... 2nd Ed. Raj Kamal Pearson Education

## **ARM7TDMI**

- Design centers around and concentrate on simple instructions

- Smaller and simpler processor circuit, Simpler decoding sub-unit.

- Lower power– more space for other performing units

#### A three stage pipeline

| <b>STAGE 1</b> | Instruction A | Instruction B   | Instruction C          |

|----------------|---------------|-----------------|------------------------|

|                | Execute       | Execute         | Execute                |

| <b>STAGE 2</b> | Instruction B | Instruction C   | Instruction D          |

|                | Decode        | Decode          | Decode                 |

| STAGE 3        | Instruction C | Instruction D   | Instruction E          |

|                | Fetch         | Fetch           | Fetch                  |

|                | clock cycle n | clock cycle n+1 | <u>clock cycle n+2</u> |

#### Time

#### Pipeline

Three stage Pipelining in superscalar processor facilitating each instruction fetch is in single cycle, decoding in single cycle and execute in the single cycle: Three times execution speed boost up

#### Buses

- ARM 7 common internal bus for the address and data of 32-bit in-32-bit Princeton architecture bus and bus interface for 32-bit data and instructions.

- ARM9 Harvard Architecture.

- Uses 0.25µm and less die size HCMOS technology

- Very small die size facilitating low voltage operations and low power consumption

- Very small power consumption means very low MIPS/Watt

7

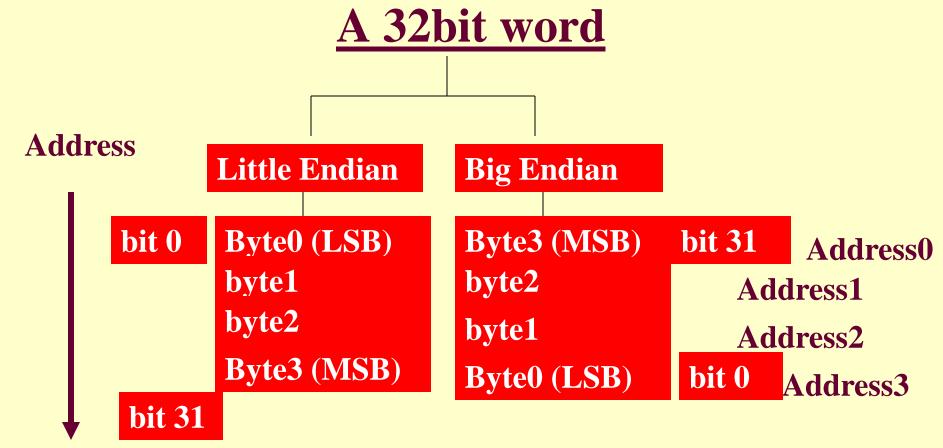

• Processor operation on the words as per initialization. A word alignment can then be in *big* endian [least significant byte stored as higher bits (address 3) of a word] or little endian [least significant byte stored as lower bits (address 0) of a word].

#### **Two Initialization options**

Fully static operation- MCU clock can be reduced to 0 and since fully MOSFETs based

- Optimized for fast interrupts and DSP algorithms

- There are two types of requests for interrupts- Fast interrupt request (FIQ) and interrupt request (IRQ). Fast means high priority.

4 gigabytes of linear address space

32-bit large set of 16 generalpurpose registers with program counter as one of the register (r15) plus CPSR and SPSR -are two other registers.

#### Features

Coprocessor interface to connect coprocessors, like DSP processors and Java Accelerators

#### Features

- System control functions implemented in standard lowpower logic

- Cost-effective, compact chip

## ARM 7 T Variants

#### ARM® TDMI<sup>TM</sup> instruction set options-

# 1. High-performance 32-bit instruction set-

2. High-code-density Thumb®16-bit instruction set than 32-bit instruction architecture

# Summary

Microcontrollers-... 2nd Ed. Raj Kamal Pearson Education

## We learnt

- 32 bit Sixteen Registers plus CPSR and SPSR

- ARM 9 and ARM7 Harvard and Princeton architectures

- Initialized options: little or big endian modes

## We learnt

- 32/16/8 bit data types

- Two interrupts Fast interrupt request (FIQ) and interrupt request (IRQ)

#### End of Lesson 2 on ARM7 Architecture