## Chapter 14

## 80x96 Family Microcontrollers

## Lesson 1

## 80x96 Architecture overview

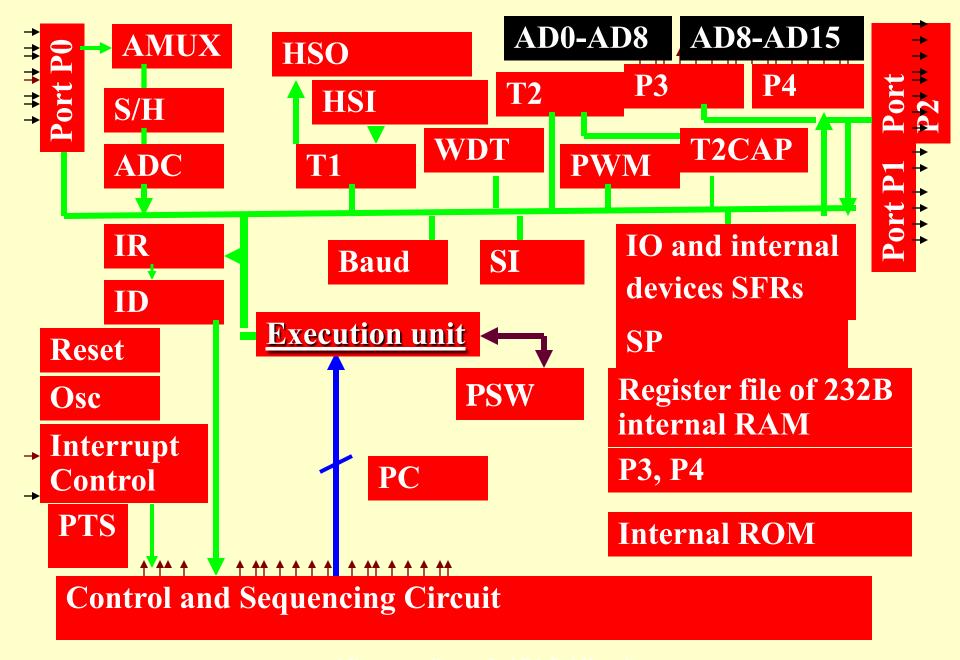

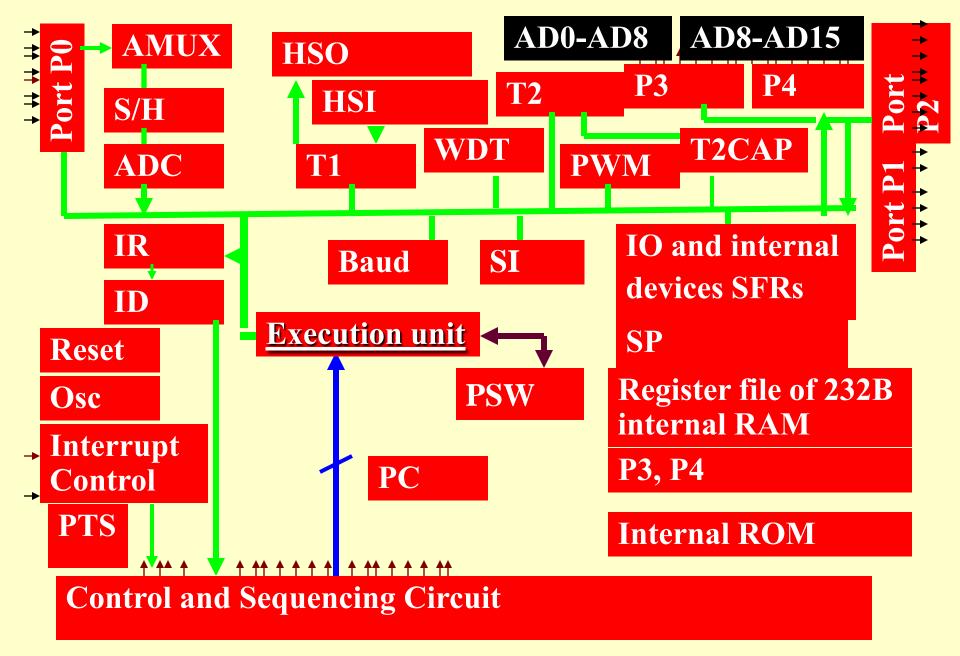

## **CPU Performance**

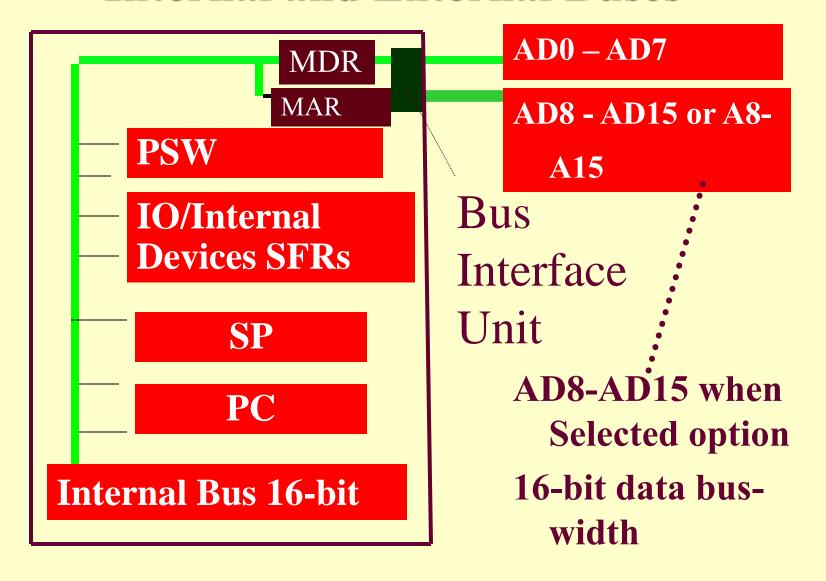

- 16-bit internal bus and 16 bit address

- 16/8 bits (selectable options) external data bus

- Result in higher processing rate than an 8-bit CPU

- 12/16 MHz XTAL- High clock rate

#### **Internal and External Buses**

## **CPU Registers**

- 16-bit Program Counter PC

- 16- bit PSW (Processor Status Word)

- 16-bit Stack Pointer <u>SP</u> (Also a memory address)

- A 16-bit Register lower byte saves in memory at even and upper byte at odd address) [Little Endian Word alignment]

## 16-bit word alignment

### A 16bit word in memory

Little Endian

Address

Byte0 (LSB)

Address0

Byte1 (MSB)

Address1

## **PSW**

- Z Zero flag

- N Negative Flag

- Overflow flag

- Overflow trap flag

- Carry flag

- Primary interrupt enable bit

- ST Sticky bit flag

#### **PSW.15-PSW.8**

**PSW**

#### PSW.7-PSW.0

**Z PSW.15**

PSW.7

N

**PSW.14**

V

**PSW.13**

VT

**PSW.12**

C

**PSW.11**

**PSW.10**

Ι

PSW.9

ST

PSW.8

PSW.0

Secondary

Interrupt

Mask

bits

#### **CPU Instructions**

- .16 as well as 8-bit data type Instructions

- Processor operation of 16-bit data type is as per word alignment at memory in *little endian* [least significant byte stored as lower bits (address 0) of a word]

#### MCU Architecture overview

- 80x96 common 16-bit internal bus for the 16-bit addressing and 16/8-bit data

- Princeton architecture bus

- Bus interface for 16-bit/8-bit data and instructions

## <u>16-bit SP</u> Address – 0018H

**SPL**

**SPH**

Byte Address – 0018H

Byte Address – 0019H SP

Increases

before

push,

decreases

after pop

### Interrupts

• Two Maskable Interrupt requests EXINT1 at P0.7 Interrupt and EXINT and one unmaskable (NMI) interrupt

## Program Counter

• Program Counter (PC) initializes at 2080H-2081H on Reset

#### **Timers**

- Timer T1 as a free running counter

- An additional timer T2 with reset external clocking inputs

## Watchdog Timer

A watchdog timer

#### Serial Interface

• Serial Interface SI-option UART full duplex or half duplex serial synchronous bits with separate clock bits

## High Speed Output on compares

HSO High speed outputs

## High Speed Input Captures

HSI High Speed inputs

#### ADC

Multi channel ADC

## 80x96 Architecture view

# 64 kB address space with H and V windows Memory Architecture

80x96 **Internal** Address devices IO and internal Registers devices SFRs, SP **Data and** and Registers as Program, **Internal RAM** constants, stored Internal ROM, tables External RAM/ Common **External ROM Memory**

#### 80x96 Family Programming Model **Horizontal** and PC, PSW Vertical Windows IO and internal **Address Space** for 8-bit devices SFRs, SP addressing **Internal RAM** Register file ROM, RAM Linear 16-bit addresses

## Horizontal and Vertical Windows for 8-bit addressing

H and V windows Page 0 addressable by 8bits for 0000H-00FFH Internal RAM can be used as registers

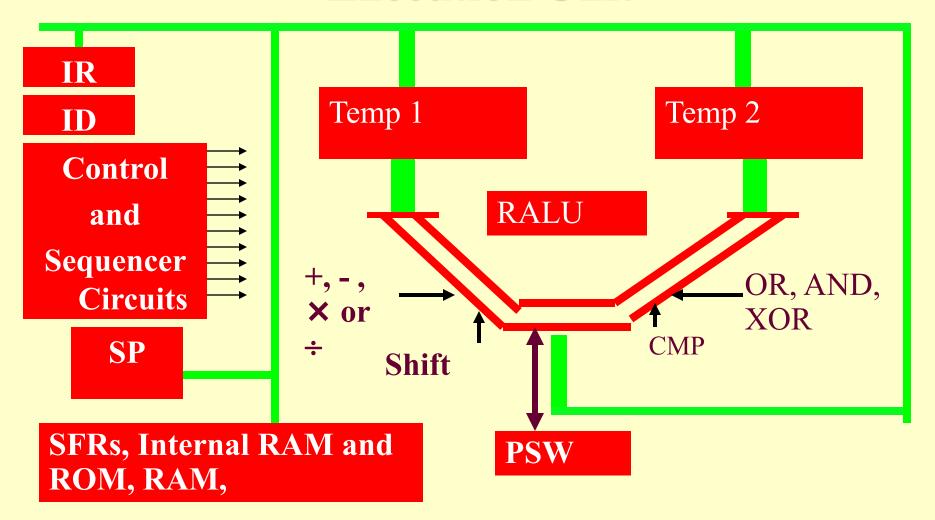

#### **RALU**

• *multiplier* and *divide*

#### **Execution Unit**

### **Instruction Execution**

STAGE 1

Instruction Fetch

Instruction

Decode

<u>clock</u> <u>cycle (s)</u>

STAGE 2

STAGE 3 to n

Instruction Execute

**Time**

## Internal bus Fetch IR ID Decode **Control** Execution

and

Sequencer

**Circuits**

Control memory micro codes based-Implementation

#### Ports

Expanded Mode used for interfacing External Memory and Ports P0 to P4

## Summary

#### We learnt

- 80x96 family 16-bit processor

- <u>PC</u>, <u>SP</u>, PSW

- Princeton architecture

- 16/8 bit data types

- Little endian 16-bit word alignment

- Interrupts Maskable Interrupt requests (EXINT, EXINT1) and unmaskable (NMI)

- PC = 2080H at reset

#### We learnt

- IO/Devices Control and Status SFRs, SP, Internal RAM – H and V windows 8-bit addressing

- Internal ROM

- RAM/ROM

#### We learnt

#### **Internal Devices**

- T1free running counter and T2

- SI

- HSOs

- HSIs

- Multi channel ADC

# End of Lesson 1 on 80x96 Architecture overview