### Chapter 7

# System Design: Peripheral ICs and Interfacing

#### Lesson 7

#### I<sup>2</sup>CBus Interface

#### **Serial Bus**

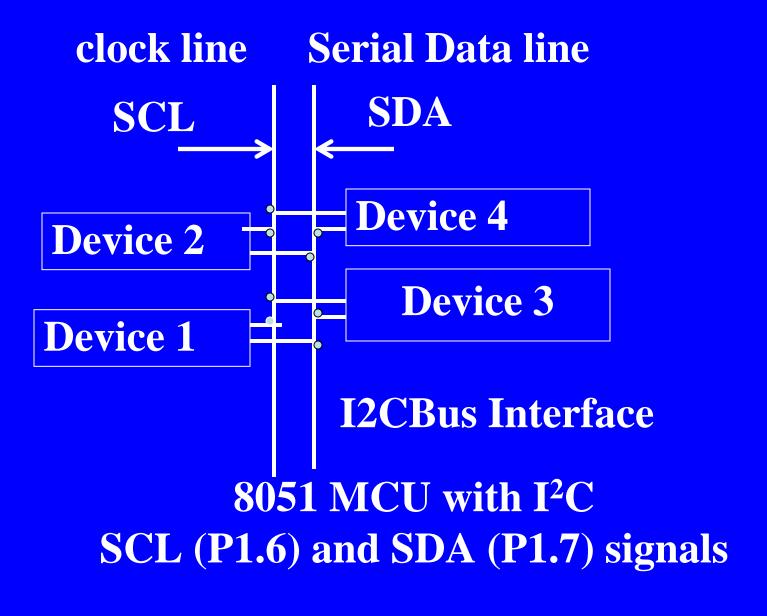

- Serial bus connects several devices through common lines

- Only addressed device receives (accepts) the line output from communication device at an instance

#### **Serial Bus**

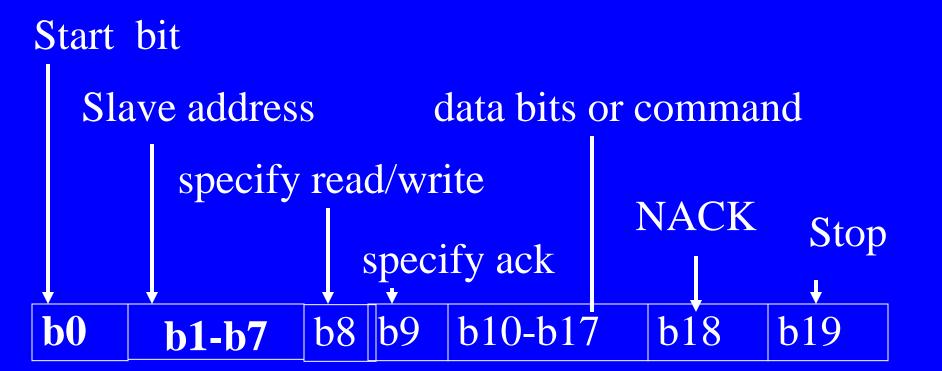

- Communicates bits for data and protocol bits at a defined rate

- Some Protocol related bits precede the data bits

- Some Protocol related bits succeed the data bits

#### **Master-Slave Communication**

- Master at I<sup>2</sup>C serial synchronous bus sends clock pulses SCL and data bits SDA

- Slave receives bits after synchronizing the SCL clock

#### I<sup>2</sup>C Bus Protocol and Data Serial line bits

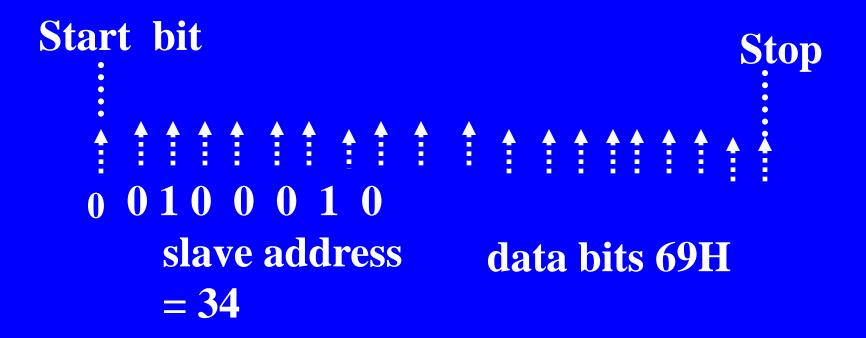

#### SDA (Serial Data) line in I<sup>2</sup>C

**Data bits (10100100) 20T format**

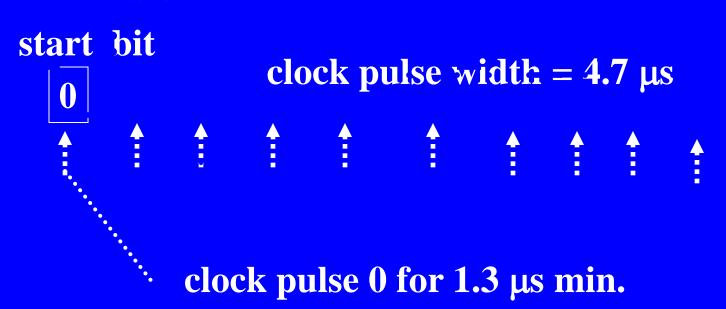

#### Timings of Ten clock pulses

SCL at slave address

SCL(Serial Clock) serial line in I<sup>2</sup>C

## Summary

## We learnt I<sup>2</sup>C

- A serial synchronous bus -two lines SCL and SDA

- Interconnects 128 devices

- 20 bits per byte communication

- Start and stop bits