**Chapter 4**

#### 8051 Family Microcontrollers Instruction Set

#### Lesson 3

#### **Data Transfer Instructions**

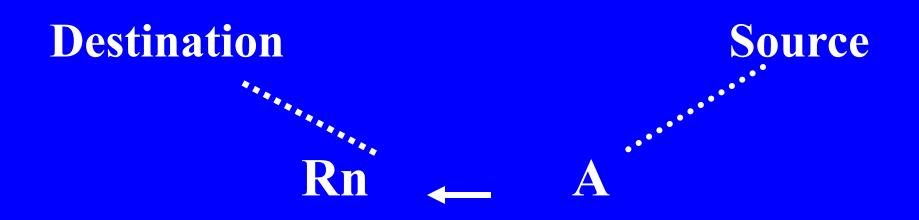

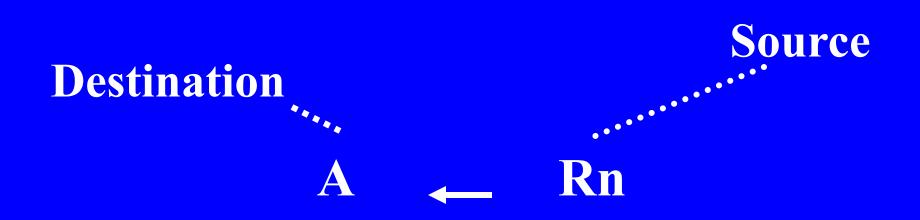

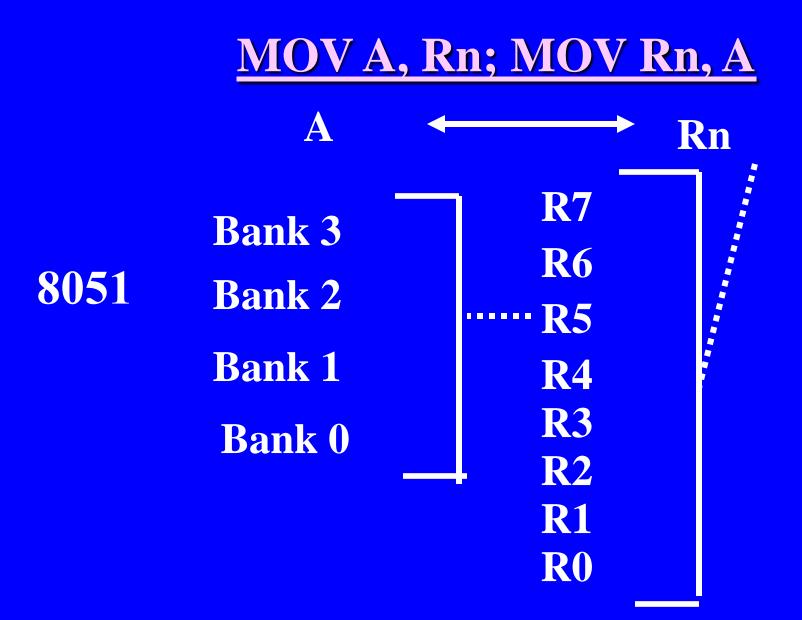

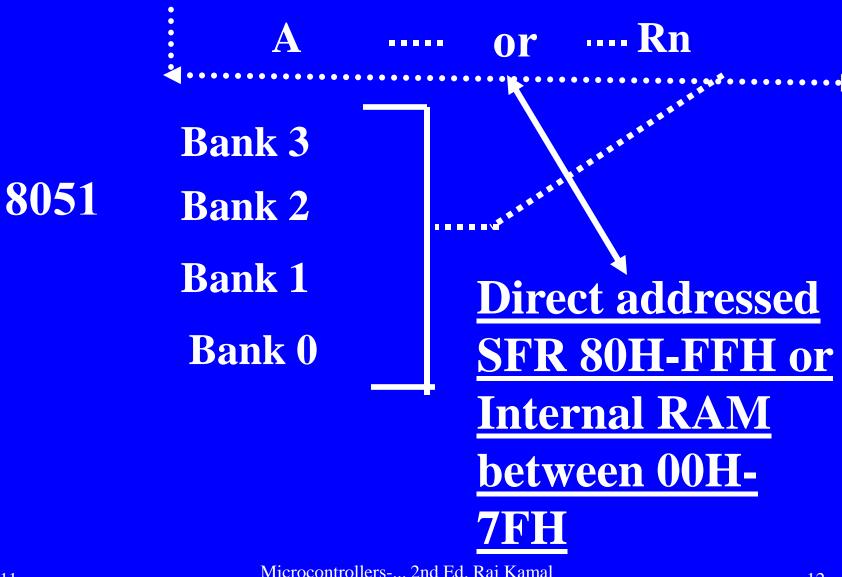

#### **Move byte between accumulator (an SFR) and register at a register bank**

#### Rn

Rn: n = 0, 1, 2, 3, 4, 5, 6, or 7,n is as per 3 bits coexisting with 5-bits with opcode

Register *n* is at the bank defined by RS1 and RS0 at PSW

- 00 means Bank 0, -01 bank 1

- 10 bank 2- 11 bank 3

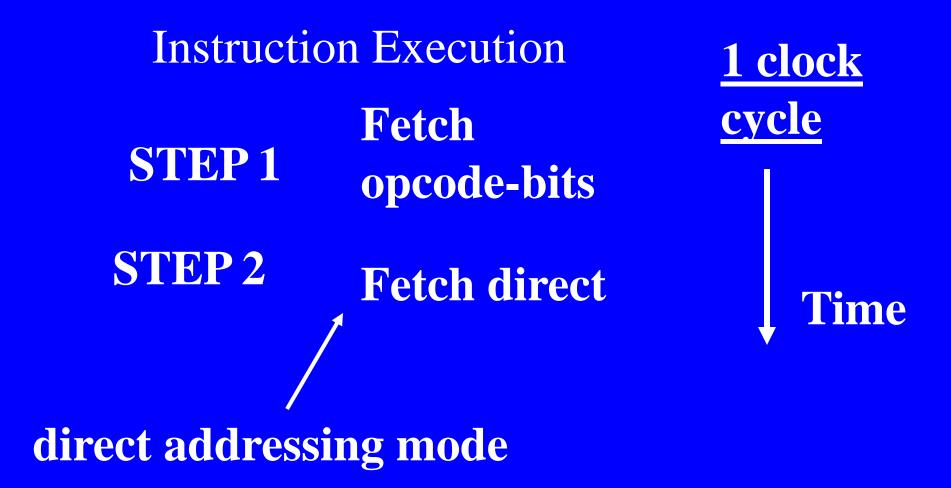

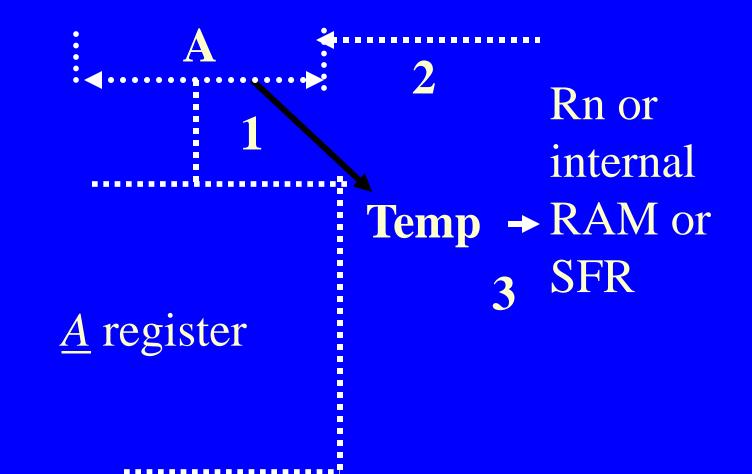

**Instruction Execution** 1 clock cycle Fetch **STEP 1** opcode-bits **Fetch bits STEP 2** Time for getting the **operand(s) Register addressing mode**

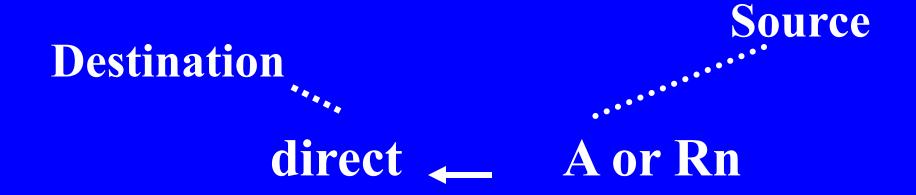

#### <u>Move byte from an SFR/Internal RAM</u> to another *direct*

#### MOV A, direct; MOV Rn, direct; MOV direct, A; MOV direct, Rn

#### An SFR or Internal RAM between 00H-7FH

#### An SFR or Internal RAM between 00H-7FH

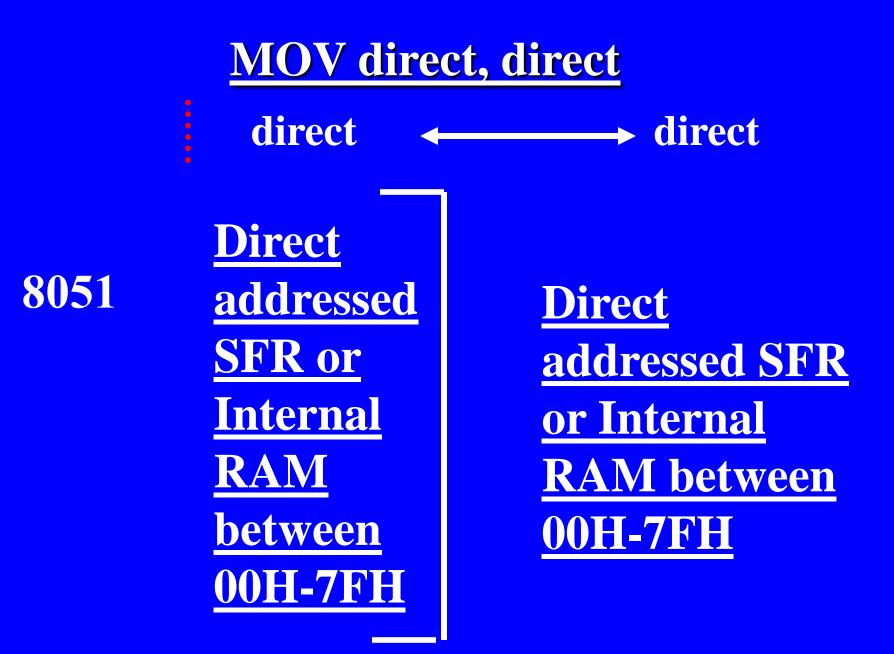

#### **MOV direct, direct**

| Instruction Execution                      |                                                                                   | 20        | <u>clock</u>   |

|--------------------------------------------|-----------------------------------------------------------------------------------|-----------|----------------|

| <b>STEP 1</b>                              | Fetch<br>opcode-bits                                                              | <u>Cy</u> | <u>cles</u>    |

| STEP 2<br>STEP 3<br>both the oper<br>modes | <ul> <li>Fetch direct</li> <li>Fetch direct</li> <li>ands using direct</li> </ul> | ct addr   | Time<br>essing |

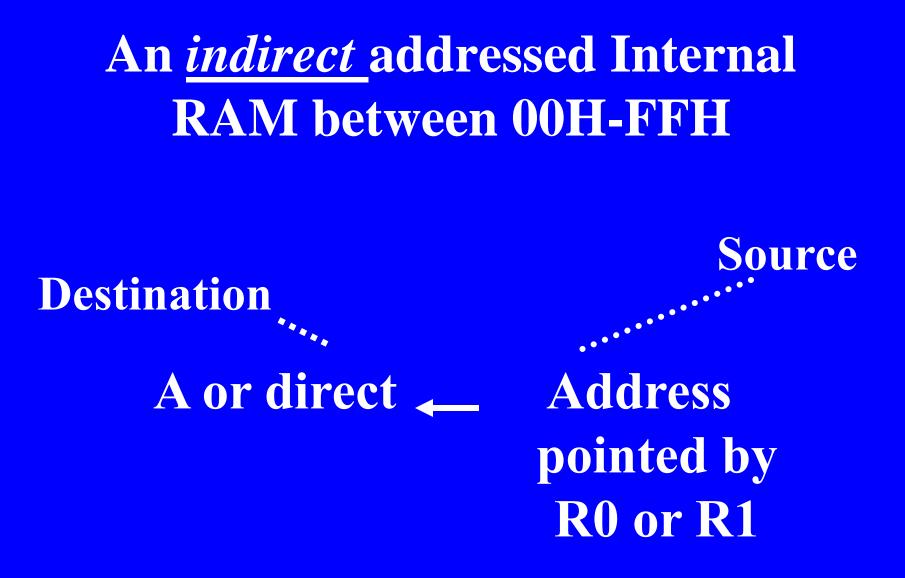

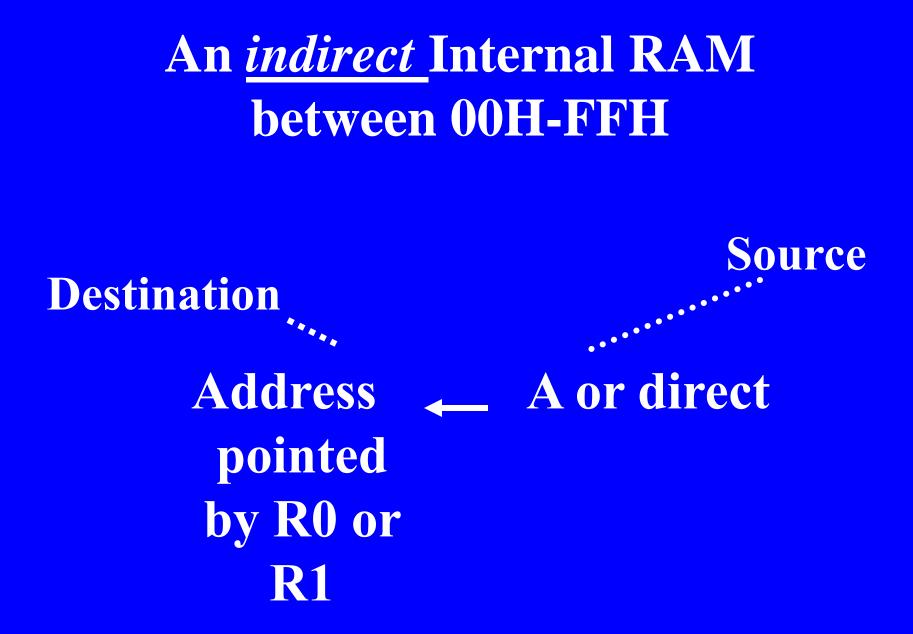

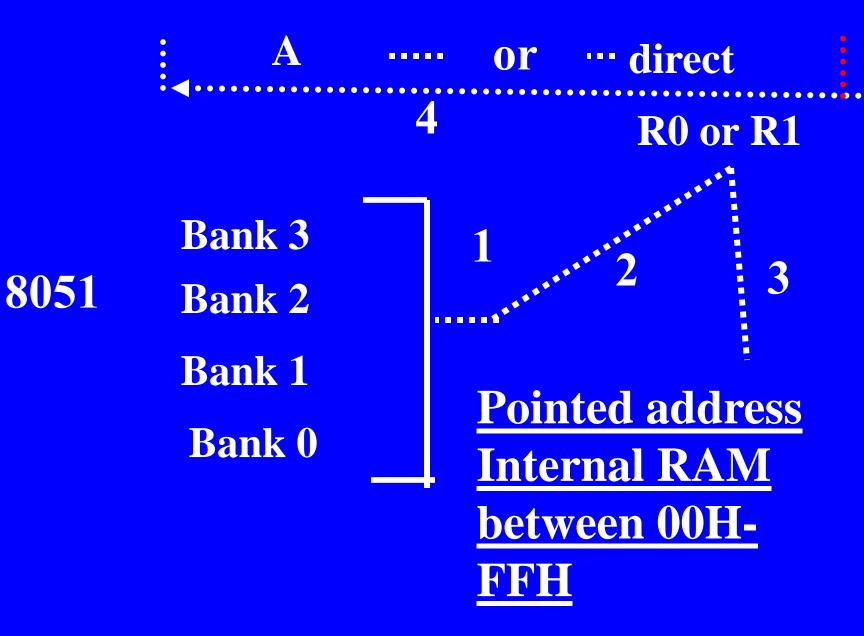

MOV A, @Ri; MOV @Ri, A; MOV direct, @Ri; MOV @Ri, direct

#### Indirect addressed Internal RAM between 00H-FFH

SFR direct addressed between 80H-SFH or A register

| Instruction Execution                |                               | <u>1 o</u>                      | or 2 |  |

|--------------------------------------|-------------------------------|---------------------------------|------|--|

| <b>STEP 1</b>                        | Fetch<br>opcode-bits          | <u>clock</u><br><u>cycle(s)</u> |      |  |

| <b>STEP 2</b>                        | Fetch bits for A<br>or direct |                                 |      |  |

| STEP 3                               | Fetch bit for i 0<br>or 1     |                                 | Time |  |

| indirect addressing mode one operand |                               |                                 |      |  |

2 cycles when direct, 1 when A other operand

#### **Instruction Execution**

# **1. No indirect addressing in 8051 instruction for an SFR**

2. Only indirect addressing in 8052 instruction Internal RAM between 80H-FFH

#### Move *immediate*, MOV immediate DPTR

#### A register

Α

2nd Byte of instruction

### For moving **08H into A** register

**MOV A,#data Example Fetch** opcode and then byte for getting the operand for move

<u>MOVA, #08H</u>

Sign # specifies that 08H is the immediate succeeding byte is the operanders-... 2nd Ed. Raj Kamal Pearson Education

Codes in Memory-74H, 08H

Rn (R0 or R1 or ...R6 or R7) at Bank 0 or 1or 2 or 3

## 2nd Byte of instruction

MOV Rn,#data Fetch opcode and then byte for getting the /operand for

Sign # specifies that 08H is the immediate succeeding byte is the operand ers-... 2nd Ed. Raj Kamal Pearson Education Codes in Memory-78H-7FH, 08H

For moving 08H into direct

MOV direct,#data Fetch opcode and then bytes for getting the operands

MOV direct, #08H

Sign # specifies that 08H is the immediate succeeding byte is the operand

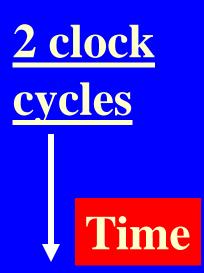

2 clock cycles

Time

Codes in Memory-75H, 00H-FFH, 08H

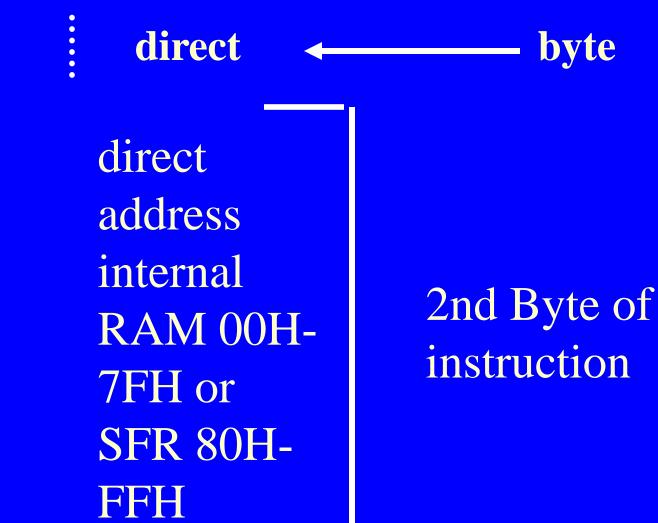

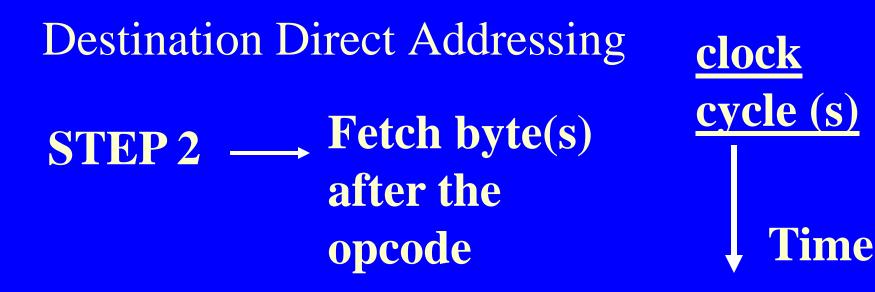

Addressing mode specifies that fetch byte(s) (next to the opcode of 8 bits) specify an address, destination operand is at that address.

#### For moving 08H into indirect

MOV @Ri,#data ng Fetch opcode → and then bits for getting the operands

### 1 clock cycle Time

MOV @Ri, #08H

Sign # specifies that 08H is the immediate succeeding byte is the operanders... 2nd Ed. Raj Kamal Pearson Education Codes in Memory-76-77H, 08H

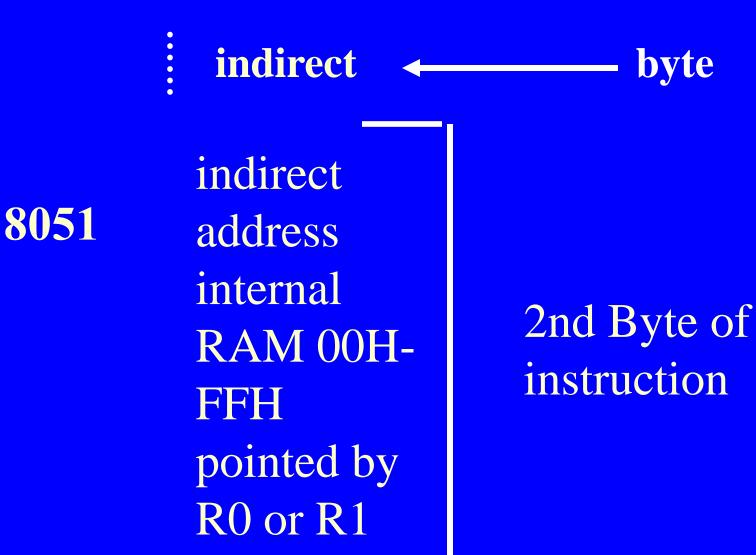

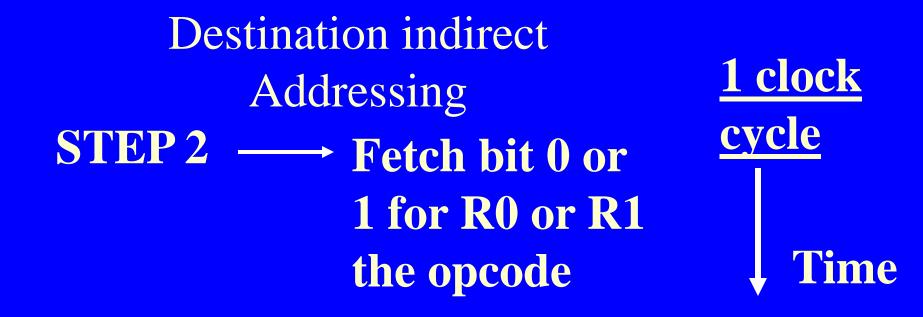

#### Addressing mode specifies that fetch byte(s) specify by an address pointed by R0 or R1 at a bank

# Immediate Addressing Four type of instructions

- A

- Rn

- direct for Internal RAM in between 00H to 7FH or direct for SFR 80H-FFH

- Indirect using R0 or R1

Immediate addressing mode for source two-bytes

Lower byte is second byte of the instruction and is for DPL

Higher byte is third byte of the instruction and is for DPH

MOV DPTR, #data16 2 clock **Fetch opcode** cycles For moving  $\rightarrow$  and then 16 **08C1H into** bits for getting Time DPTR the operands Codes in MOV DPTR, #08C1H Memory-90H, C1H, Sign # specifies that 08C1H is two immediate succeeding bytes as the operand lers-... 2nd Ed. Raj Kamal 39 **Pearson Education**

## **MOVC and MOVX indirect**

1. Only indirect addressing in 8051 instruction for a byte in external data memory

2. Only indirect addressing in 8051 instruction for a code in internal/external program memory

Always Indirect Addressing mode Internal/External Program Memory (max. 64kB)

External Data Memory and Ports (max 64kB)

MOVC A, @A + PC2 clock cycles For **Fetch opcode** transferring bits addressed C means code Time code byte memory is used **STEPS 2-3** into A MOVCA, @A + PCCode bits in Memoryindirectly specify, PC16-bits adds **83H** with 8-bits at A register and then new 16-bits point to the code at that address Microcontrollers-... 2nd Ed. Raj Kamal 43 **Pearson Education**

#### MOVC A, @A + DPTR2 clock cycles For transferring **Fetch opcode** addressed bits Time code byte **STEPS 2-3** into A MOVCA, @A + DPTR Code bits in Memory-indirectly specify, DPTR16-bits **93H** adds in 8-bits at A register and then 16-bits point to code at that C means code address memory is used Microcontrollers-... 2nd Ed. Raj Kamal

**Pearson Education**

#### MOVX A, @DPTR

For transferring an external byte into A

Fetch opcode Sign @ means DPTR is a pointer

MOVX A, @DPTR X specifies external memory, byte at DPTR points indirectly to the address for the operand

2 clock cycles Time **STEP 2** Code bits in Memory-

#### MOVX @DPTR, A

For transferring <u>A</u> to a byte at external pointed address

**Fetch opcode** Sign @ means DPTR is a pointer

MOVX @DPTR, A X specifies external memory, byte at DPTR points indirectly to the address for the operand

2 clock cycles Time **STEP 2** Code bits in Memory-

#### MOVX A, @Ri

For transferring an external byte into A

Fetch opcode Sign @ means Ri is a pointer

MOVX A, @Ri

X specifies external memory, byte at Ri points indirectly to an external memory address for the operand 2011 Microcontrollers-... 2nd Ed. Raj Ka

2 clock cycles Time **STEP 2** Code bits in Memory- E2-

#### MOVX @Ri, A

For transferring <u>A</u> to a byte at external pointed address

Fetch opcode Sign @ means Ri is a pointer

MOVX @Ri, A X specifies external memory, byte at Ri points indirectly to the address for the operand

Code bits in Memory- F2-<u>F3H</u>

### Push or Pop *direct* or Exchange or Swap

## Always direct Addressing mode for Push or Pop

## Internal data Memory (00H-7FH)

#### SFR (80H-FFH)

#### 8051

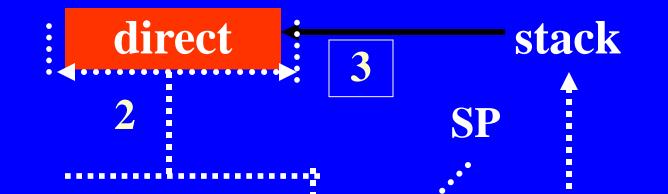

Direct address SFR or internal 00-7FH RAM

direct

••••••

•

Increment SPMove the byte to SPpointed address3

stack

and a second

SP is of 8-bits

SP

#### **Push** direct

4

8051

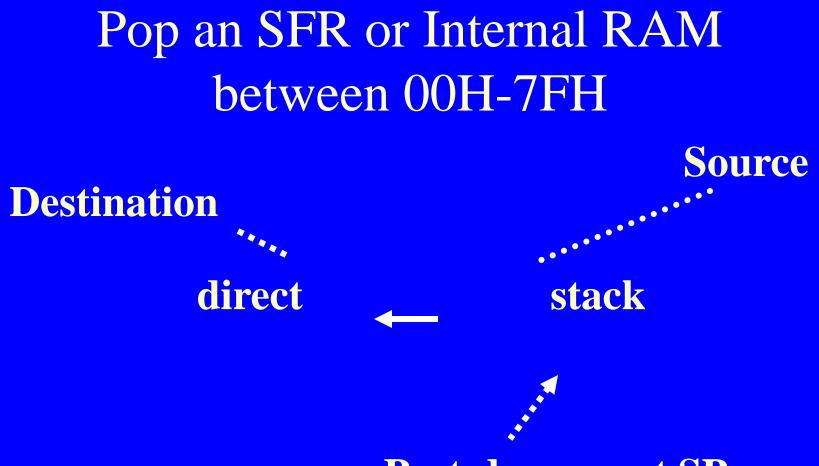

Direct address SFR or internal 00-7FH RAM Move the byte to SP pointed address and decrement SP 4

SP is of 8-bits

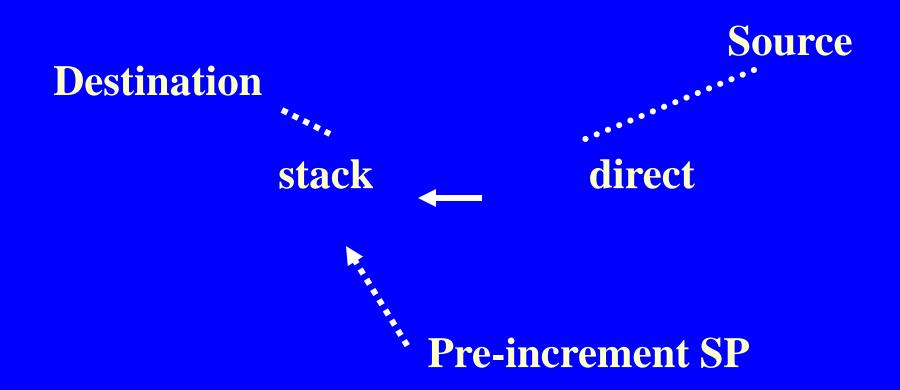

#### Pop direct

#### direct addressing mode for source operand in push and for destination operand for pop

### Push an SFR or Internal RAM between 00H-7FH

#### **Post-decrement SP**

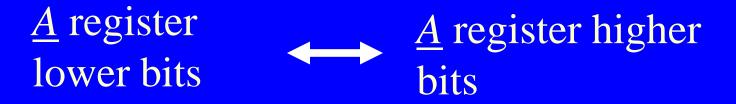

# Exchange of A register byte with other

# A register Internal data Memory (00H-FFH) ← SFR (80H-FFH)

## XCHA, Rn, XCHA, *direct*, XCHA, @Ri; exchange bytes

Microcontrollers-... 2nd Ed. Raj Kamal Pearson Education

8051

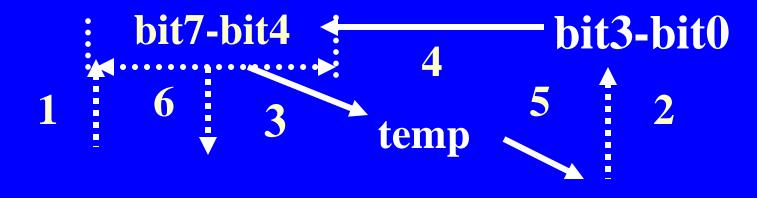

## Exchange of A register lower digit with other

# <u>A</u> register Internal data Memory (00H-FFH) ← SFR (80H-FFH)

8051

Indirect address internal 00-**FFH RAM** pointed by **R0 or R1** ......

bit3-bit0

•

A register lower 4 bits

3

temp

bit3-bit0

1

XCHDA, @Ri; exchange lower digits (4-bits)

# Exchange of <u>A</u> register lower digit with higher digit

#### 8051

A register lower 4 bits

A register higher 4 bits

#### SWAPA; exchange of lower digit (4bits) with higher at <u>A</u>

## Summary

We learnt 8051 family data transfer instructions

- move (copy)

- push

- pop

- exchange

- exchange lower 4-bits