#### Chapter 3

### 8051/8031 Family Architecture

#### Lesson 2

# 8051 Family MCUs Memory

## **Internal and External Memory**

#### **Internal memory**

- 8-bit address Internal RAM Memory

- 16-bit address Internal ROM Program memory

- SFRs are separate and have 8-bit address each in separate space from internal RAM

#### External memory

- 16-bit address Data Memory

- 16-bit address Program memory

# Internal Memory Harvard Architecture Internal Program EA Memory (4kB) addresses used when EA = 1

Internal Data Memory

- •128 B 8051

- •256 B 8052

#### External Data Memory Architecture

8051 special feature

64 kB separate address spaces for data memory

# Internal/External Program Memory Architecture

#### **Program Memory Architecture**

**Address**

**Internal ROM**

For address 0000H-0FFFH and EA = 1 (External disable)

Address

**External ROM**

For address 0000H-0FFFH

when  $\overline{EA} = 0$  (External Enable)

Program, constants and stored tables

Memory

**Address**

**External ROM**

For address 1000H-FFFFH and

$$EA = 0 \text{ or } 1$$

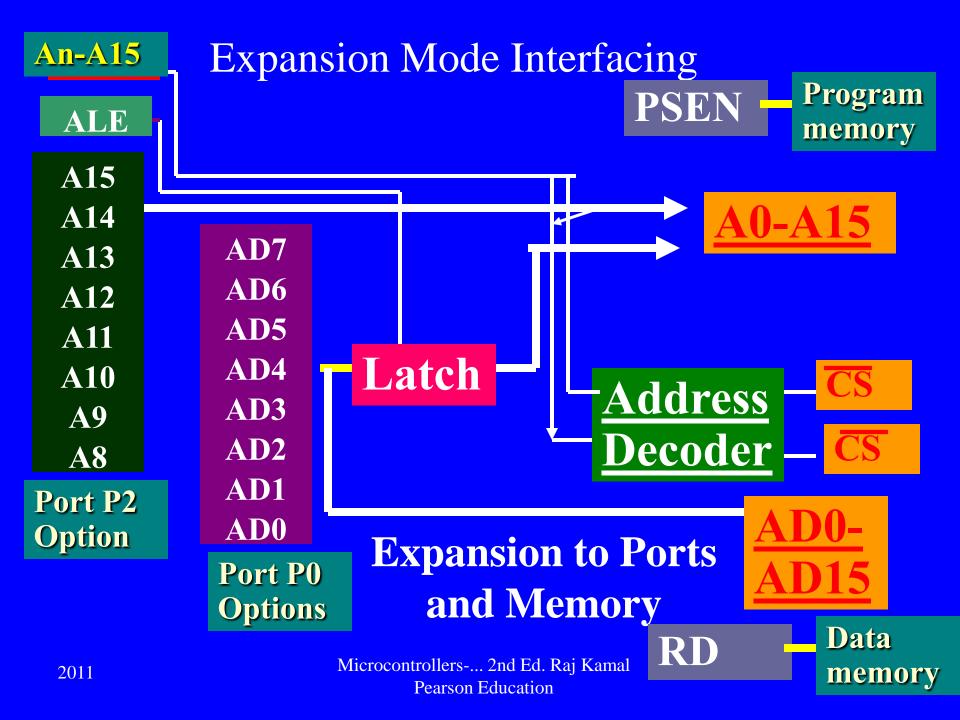

# Expansion to external memory and ports

## Expanded Mode used for interfacing

- External Data Memory and Ports and

- External Program memory

# On-Chip/Off-Chip Memory Addresses

#### SFRs 80H-FFH

- Used for IO and internal devices

Control and Status

- CPU Registers

- Not the part of Internal RAM

On-Chip SFR and Memory Addresses 8051/52 P0,..., P3

Address Space 80H-FFH IO and internal Devices SFRs

**System SFRs**

P0,..., P3, SBUF, SCON, TCON, TMOD, TL0,TH0, TH1,TL1

A, B, DPTR, PCON, PSW, SP, IE, IP

#### Memory Access by Direct Address

**80H-FFH**

IO and internal devices Control and Status Registers

SP and DPTR, IP,IE,...

00H-7FH

**Internal RAM**

8-bit addresses 00H to FFH

#### **Memory Access by Indirect**

Address

80H-FFH

Additional Internal RAM 8052

00H-7FH

**Internal RAM 8051**

8-bit addresses 00H to FFH

## On-Chip Memory Architecture Internal Data Memory RAM

8051

**Byte Address**

30H-7FH

Internal RAM 30H-7FH

20H-2FH

**Internal RAM 20H-2FH**

18H-1FH

10H-17H

08H-0FH

00H-07H

Register Bank 3

Register Bank 2

Register Bank 1

Register Bank 0

Each bit also addressable Bit addresses 8-bit each 00H -7FH

Data Memory

Internal RAM as the Register Banks

#### Register Banks of 8 registers each

- Each Byte at the register Ri (R0 orR1) in a register-bank can be used as pointer to an 8-bit indirect addressing

- Each Byte at the register R0, .., R7 (Rn) can be used for a variable with 3 bits in instruction defining n and RS0 and RS1 at PSW defining the bank 0, 1, 2, or 3.

#### **Off-Chip Memory Addresses**

8051

0000H-FFFFH **External RAM Data Memory**

0000H-FFFFH **External ROM Program**

Memory when  $\overline{EA} = 0$

1000H-FFFFH **External ROM Program**

Memory when EA = 0 or 1

#### External RAM in 8051

0000H-00FFH →

01FFH-FFFFH page0 external RAM, indirect addressable by R0 or R1 or by indirect 16-bit address

**Indirect 16-bit address**

Off-Chip Data Memory Architecture

#### **Program Memory Architecture**

0000H-0002H -

Initial 3-byte instruction for branch

0003H-0032H, 0053H-

**005BH**

ISRs of maximum 8 bytes each

005CH-FFFFH User Program, constants, stored tables

**ROM in 8051**

# On-Chip/Off-Chip Memory Addresses in extended 8051

#### Extended 8051

**External ROM**

RICHRICH

.

External

ROM

RRRRE

010000H

1000H

FFFFFFH

010000H

RECEIPT

1000H

Internal ROM

0000H-0FFFH

**ECODE**

External RAM

**External RAM**

Internal RAM

SFR

00H-7FH

80H-FFH

**Extended XDATA**

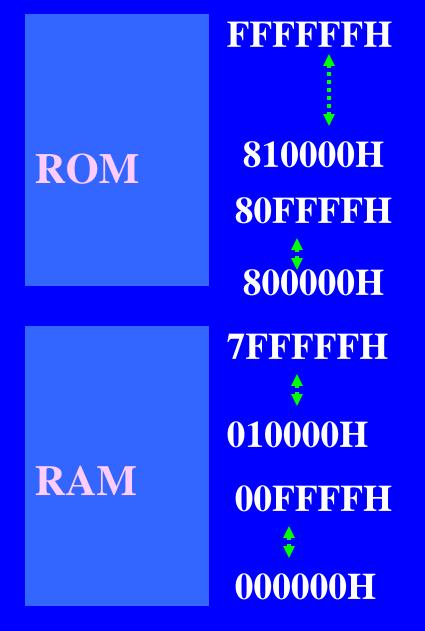

## Philips 8051MX

Unified Internal and External Addresses

Princeton

Architecture

## Philips 8051MX

**External ROM**

**External**

ROM

REFERENCE

810000H

80FFFFH

800000H

7FFF00H

010000H

**OOFFFFH**

000000H

Internal ROM

0000H-0FFFH

**ECODE**

**Extended XDATA**

External

**RAM**

SFR

**7FFF80H**

7REF7EH

700000

**External RAM**

Internal RAM

7FFF00H

rollers-... 2nd Ed. Raj Kamal Pearson Education

## Summary

#### We learnt

#### SFRs and memory

- SFRs

- Internal RAM with bit addressable RAM and four register banks

- External RAM Harvard Architecture

- Internal Program Memory Harvard Architecture

- External Program Memory Harvard Architecture

#### We learnt

#### memory

- Extended Memory in Extended 8051 version

- Unified Memory space in 8051MX