### Chapter 05: Basic Processing Units ... Control Unit Design Organization

Lesson 06:

Performing an Arithmetic or Logical

Operation

### **Objective**

• Learn how an arithmetic or logic operation performed by sequences of microoperations

### **Arithmetic or logic operation**

# **Execution of an ALU Instruction by Data**Path Implementation

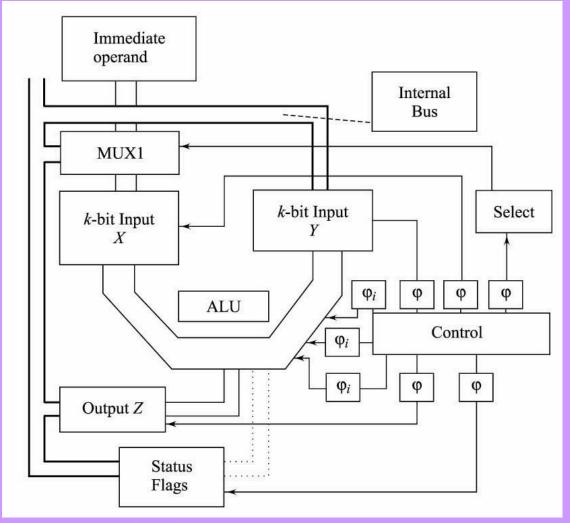

- Execution of an ALU instruction can be considered as the implementation of a specific data path flow, as per the specific ALU instruction

- The processing unit composition is as controlled data-path unit and control unit (controlling and sequencing unit)

- Control unit generates control signals to implement each step using signals φs

# Sequence of actions to define the controlled transfers of data between processing subunits

- Processing subunits—registers, X, Y, ALU circuits, Z, and status register along a required data path

- MUX unit to select one data path among several

# ALU design as data path with a control unit for arithmetic or logic operation

Schaum's Outline of Theory and Problems of Computer Architecture Copyright © The McGraw-Hill Companies Inc. Indian Special Edition 2009

### Microoperations after receiving the instruction at IR

- Decoded by decoding logic

- Then the logic results at register instruction decoder (ID) initiate control actions

- Each control signal selects an action through a gate input  $\phi$  at each step

- 1. Step i: Transfers a k-bit input source operand through the bus or immediate operand to X Input operand through a MUX  $\rightarrow$  X

- MUX— a multiplexer to select one among several channels at inputs as per the select subunit signal

2. Step i + 1: X transfers k-bit input X to ALU— $X \rightarrow ALU$

3. Step i + 2: Another input operand transfers k-bits to Y (through bus)—Input operand  $\rightarrow Y$

4. Step i + 3: Transfer Y to ALU—  $Y \rightarrow$  ALU

5. Step i + 4: ALU processing unit select through one of the gates  $\phi_i$  an operation as per the arithmetic or logic instruction, which was received at the IR

6. Step i + 5: Transfers a k-bit output Z from ALU—

$Z \leftarrow ALU$

7. Step i + 6: Transfers status flags generated, for example, carry or overflow to status register —Status Register ← ALU

8. Step i + 7: Transfers from Z the result to destination operand through bus—

$$(Bus) \leftarrow Z$$

#### **ALU** instruction

Eight steps in Z ← operation (X and Y operands), Flags ← status of operation and Bus ← Z

### **ADD** operation

#### **Add instruction**

- 1. Input operand through a MUX  $\rightarrow$  X

- $2. X \rightarrow ALU$ -input

- 3. Input operand  $\rightarrow Y$

- 4.  $Y \rightarrow ALU$ -input

#### **Add instruction**

- 5. Selects adder gate  $\phi_{add}$  when ADD instruction received at the IR and decoded at the instruction decoder logic

- $\phi_{\text{add}}$ : ALU-output  $(0-k-1) \leftarrow X + Y$

- 6.  $Z \leftarrow ALU$ -output (0-k-1)

- 7. Status Register ← ALU (status)

- 8. (Bus)  $\leftarrow$  Z

#### **SUB** instruction

- 1. Input operand through a MUX  $\rightarrow$  X

- $2. X \rightarrow ALU$ -input

- 3. Input operand  $\rightarrow Y$

- 4.  $Y \rightarrow ALU$ -input

### **SUB** operation

#### **SUB** instruction

- 5. Selects subtractor gate  $\phi_{sub}$  when SUB instruction received at the IR and decoded at the instruction decoder logic

- $\phi_{\text{sub}}$ : ALU-output (0-k-1)  $\leftarrow$  ALU  $\leftarrow$  X + NOT(Y) + 1 for finding X Y

- 6.  $Z \leftarrow ALU$ -output (0-k-1)

- 7. Status Register ← ALU (status)

- 8. (Bus)  $\leftarrow$  Z

### Control Signal for selecting an ALU operation

### ALU control input during an interval T step 5 for an Arithmetic Operation

- One active C<sub>alu</sub> among eight φs for eight arithmetic operations

- 1.  $\phi_{\text{add}}$ : ALU  $\leftarrow$  X + Y

- 2.  $\phi_{\text{sub}}$ : ALU  $\leftarrow$  X + NOT(Y) + 1

- 3.  $\phi_{adc}$ : ALU  $\leftarrow$  X + Y + CY

- 4.  $\phi_{\text{sbb}}$ : ALU  $\leftarrow$  X + NOT(Y) + 1 + Cy

# ALU control input during an interval T step 5 for an Arithmetic Operation

- 5.  $\phi_{\text{mul}}$ : ALU  $\leftarrow$  X  $\times$  Y

- 6.  $\phi_{\text{div}}: \text{ALU} \leftarrow X \div Y$

- 7.  $\phi_{\text{inc}}$ : temp\_Y  $\leftarrow$  1; ALU  $\leftarrow$  X + temp\_Y

- 8.  $\phi_{dec}$ : temp\_Y  $\leftarrow$  1; ALU  $\leftarrow$  X + NOT( temp\_Y) + 1

# ALU control input during an interval T step 5 for a Logic Operation

- One active C<sub>alu</sub> among six φs for six logic operations

- 1.  $\phi_{XOR}$ : ALU  $\leftarrow$  X .XOR. Y

- 2.  $\phi_{OR}$ : ALU  $\leftarrow$  X.OR. Y

- 3.  $\phi_{AND}$ : ALU  $\leftarrow$  X .AND.Y

- 4.  $\phi_{NOT}$ : ALU  $\leftarrow$  NOT (X)

# ALU control input during an interval T step 5 for a Logic Operation

- 5.  $\phi_{\text{clear}}$ : ALU  $\leftarrow$  all 0s

- 6.  $\phi_{\text{set}}$ : ALU  $\leftarrow$  all 1s

### Summary

#### We learnt

- An arithmetic or logic operation performed by sequences of microoperations

- Eight steps for an ALU operation among 8 arithmetic and six logic operations

### End of Lesson 06 on Performing an Arithmetic or Logical Operation